Modul 3 ( Laporan Akhir 1 )

2. Alat dan Bahan

[Kembali]

3. Rangkaian Simulasi [Kembali]

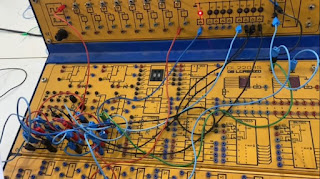

gambar rangkaian pada percobaan 1 menggunakan De Lorenzo

gambar rangkaian pada percobaan 1 menggunakan proteus

4. Prinsip Kerja Rangkaian

[Kembali]

Pada percobaan 1 ini, menggunakan rangkaian counter asyncronous, dimana vcc mengaliri switch SPDT ketika switch SPDT berlogika 1, dan juga mengaliri input J dan K pada Flip Flop yang pertama dan input CLK dihubungkan ke clock. arus dari SPDT dialirkan menuju setiap input RS pada setiap flip flop dan input JK pada setiap flip flop berikutnya. sedangkan input CLK pada setiap flip flop setelah flip flop pertama dihubungkan dengan input Q atau pun Q' Flip Flop sebelumnya, sehingga perubahan logic probe pada setiap outpiakan bergulir.

Ketika CLK Flip flop dihubungkan ke Q flip flop sebelumnya maka akan terangkai counter UP, dimana Logic Probe akan berubah dari nilai desimal terkecil (0) hingga ke nilai desimal maksimal

Ketika CLK Flip flop dihubungkan ke Q' flip flop sebelumnya maka akan terangkai counter Down, dimana Logic Probe akan berubah dari nilai desimal maksimal hingga ke nilai desimal terkecil.

5. Video Rangkaian

[Kembali]

6. Analisa

[Kembali]

Soal analisa yang diberikan ada 2 buah yakni:

1. Analisa output percobaan berdasarkan ic yang digunakan?

jawab:

Pada percobaan 1 ini IC yang di gunakan adalah IC 741512 dimana ini adalah JK Flip Flop. Outuputnya didapatkan pada saat clocknya fault time, terjadi perubahan bit dari 1 ke 0. Hal ini terjadi kerena inputan J dan K itu bernilai 1 dimana outputnya toggle. sehingga output tersebut berpindah setiap terjadi perubahan bit dari 1 ke 0 pada clock

2. Analisa sinyal output yang dikeluarkan jk flipflop kedua dan ketiga?

jawab:

Pada percobaan 1 ini, rangkainnya merupakan rangkaian asyncronous diamana, untuk rangkaian nya dipasang secara seri, JK flip flop kedua itu inputan clocknya berasal dari outpuut JK flip flop pertama, sehingga JK flip flop kedua ini harus menunggu hasil outputan JK flip flop pertama.

Begitu pun untuk Jk flip flop ketiga, dia harus menunggu outputan dari JK flip flop kedua untuk dimasukan ke inputan clock Jk flip flop ketiga. Hal ini terjadi karena percobaan 1 itu asyncronous dimana outputnya itu sendiri seri jadi percobaannya menghasilkan output yang agak lama karena harus saling menunggu output sebelumnya

7. Link Download

[Kembali]

Download HTML disini

Donwload Rangkaian Simulasi disini

Download Video Simulasi disini

Download Datasheet ic 74LS112A disini

Download Datasheet SW-SPDT disini

.png)

Tidak ada komentar:

Posting Komentar